# On Application Design for Manycore Processing Systems in the Domain of Neuroscience

Over applicatieontwerp voor manycoresystemen in het domein van neurowetenschappen

Thesis

to obtain the degree of Doctor from the Erasmus University Rotterdam by command of the rector magnificus

prof. dr. R.C.M.E. Engels

and in accordance with the decision of the Doctorate Board. The public defence shall be held on Tuesday 8 December 2020

> at 9:30 by

Georgios Chatzikonstantis born in Athens, Greece.

### **Doctoral Committee:**

prof. dr. C.I. de Zeeuw prof. dr. D. Soudris **Promotors:**

dr. Z. Gao Other members:

dr. ir. Z. Al-Ars dr. D. Pnevmatikatos

**Copromotor:** dr. C. Strydis

## Abstract

In recent years, the rapidly growing field of human neuromodelling has undergone significant changes. Neuroscientists have been taking impressive steps in unveiling the elaborate functionality of the human brain. In doing so, complex mathematical models have been the focus of efforts for describing detailed electrochemical processes that govern the human brain's behaviour. Such efforts require tremendous computational power in order to render, simulate and analyze in traditional computing systems. As such, the field of computational neuroscience presents an imposing challenge that the realm of high performance computing is tasked with meeting.

The evolution of our understanding and mapping of the human brain has been accompanied by a steady increase in the processing power made available in manycore processors. Processors such as Intel's Xeon Phi line of products have grown to incorporate more advanced computing capability over the years. Due to their nature, they also provide traditional parallel coding tools, which can significantly impact the ease at which applications can be developed, tested and marketed. As a result, manycore CPUs are presented as an attractive alternative to other high-performance computing fabrics, such as GPUs and FPGAs.

In this Doctoral thesis, we investigate the impact that manycore processors can have in the domain of computational neuroscience, specifically from the viewpoint of high-detail neuromodelling. By identifying a lack of research efforts in high-performance, large-scale, detailed neuronal simulations, the thesis presents the development of a simulator rich 'in biophysical detail in manycore x86-based processors. Furthermore, the simulator acts as a means to study how manycore processors have evolved in architecture and behaviour, as well as highlight their strengths and drawbacks, in an effort to understand the role that they can play in the landscape of high-performance neuromodelling.

This Doctoral thesis presents the complete development effort of the aforementioned simulator. The effort commences with an application specifically designed for the earliest, experimental manycore processors. We meticulously re-configure the simulator and its implementation design in order to take advantage of the continuously evolving architecture of manycore processors. Through this process, the simulator incorporates more modelling options, supports a wider range of simulation parameters and operates on a scalable, modern manycore system. The end product of this thesis is a simulator that constitutes an efficient solution for studying demanding neuronal models, in terms of both performance and energy. The thesis starts with a design that can simulate an average network of 50k neurons and 2million synapses in 40 minutes for every second of simulated brain activity; the final design on a modern, small cluster of manycore

processors vastly improves on this design by simulating 2million neurons and 2billion synapses in under 10 minutes for every second of simulated brain activity.

Our point of focus and contributions lie in the analysis of manycore processor performance when tasked with demanding neuromodelling workloads. Through the proposed simulator, we highlight how the significant wealth of neuromodelling parameters affects simulation in different manycore processors. The thesis will provide a clear map on matching the correct amount, and type, of hardware to different network simulation configurations. As such, we take an important step towards defining proper utilization of high-performance hardware in order to match simulation challenges imposed by the domain of computational neuroscience.

Furthermore, significant effort is expended in incorporating the simulator in a larger, collaborative framework aimed at serving as an online resource for high-performance neuromodelling simulations. The designed framework, named "BrainFrame", leverages a heterogeneous ensemble of accelerators, namely manycore processors, FPGAs and GPUs, in order to provide efficient solutions for different modelling and network configurations. We provide a proof of value in the framework by identifying different use cases where a switch in the underlying accelerator hardware yields significant gains in performance, thus reinforcing the value of heterogeneity in high-performance neuromodelling. In particular, the framework further highlights the value of matching the accelerating hardware of choice with the computational workload at hand by indicating differences in performance by orders of magnitude between the different accelerators examined in different network configuration scenarios.

Abstract in Greek iv

## Περίληψη Στα Ελληνικά

Στα πρόσφατα χρόνια, το ταχύτατα εξελισσόμενο πεδίο της μοντελοποίησης του ανθρώπινου εγκεφάλου παρουσίασε σημαντικές εξελίξεις. Οι νευροεπιστήμονες ανά τον κόσμο σημείωνουν εντυπωσιακά βήματα στην χαρτογράφηση του λεπτομερούς τρόπου λειτουργίας του ανθρώπινου εγκεφάλου. Στην προσπάθεια τους αυτή, αναπτύχθηκαν πολύπλοκα μαθηματικά μοντέλα τα οποία επιτρέπουν την περιγραφή και μελέτη λεπτομερών ηλεκτροχημικών διεργασιών που διέπουν τη συμπεριφορά του εγκεφάλου. Τέτοιες προσπάθειες συνοδεύονται από εξαιρετικά μεγάλα υπολογιστικά φορτία προκειμένου να προσομοιωθούν και να αναλυθούν τα απαραίτητα δεδομένα, συνήθως δε σε απλά υπολογιστικά συστήματα. Ως εκ τούτου, το πεδίο της υπολογιστικής νευροεπιστήμης παρουσιάζει επιβλητικές προκλήσεις που η επιστήμη της υπολογιστικής επεξεργασίας υψηλής ισχύος καλείται να απαντήσει.

Η εξέλιξη της κατανόησης και της χαρτογράφησης του ανθρώπινου εγκεφάλου έχει συνοδευθεί από μια σταθερή αύξηση στη διαθέσιμη υπολογιστική ισχύ που προσφέρουν οι πολυπύρηνοι επεξεργαστές. Επεξεργαστές όπως ο Xeon Phi της Intel εξελίσσονται διαρκώς ώστε να διαθέτουν αυξανόμενη υπολογιστική ικανότητα. Χάρη στον σχεδιασμό τους, προσφέρουν την ικανότητα προγραμματισμού με παραδοσιακά εργαλεία λογισμικού παράλληλης επεξεργασίας. Η δυνατότητα αυτή επηρεάζει σημαντικά την ευκολία με την οποία οι εφαρμογές λογισμικού μπορούν να αναπτυχθούν, να ελεγχθούν για την ποιότητά τους και να προωθηθούν στην αγορά. Ως αποτέλεσμα, οι πολυπύρηνοι επεξεργαστές αποτελούν μια ενδιαφέρουσα εναλλακτική οδό σε σύγκριση με άλλα εδραιωμένα συστήματα υψηλής επεξεργαστικής ισχύος, όπως οι κάρτες γραφικών και τα FPGA.

Η παρούσα διατριβή ερευνά την αποτελεσματικότητα των πολυπύρηνων επεξεργαστών στα προβλήματα που απαντώνται στον τομέα της υπολογιστικής νευροεπιστήμης, κυρίως στο κομμάτι της μοντελοποίησης νευρώνων με μεγάλο βαθμό λεπτομέρειας. Μετά την τεκμηρίωση μιας ανιχνευμένης έλλειψης έρευνας σε προσομοιώσεις μεγάλων, λεπτομερών δικτύων νευρώνων σε υψηλής επεξεργαστικής ισχύος συστήματα, η διατριβή παρουσιάζει την ανάπτυξη ενός προσομοιωτή με έμφαση στη μοντελοποίηση βιοφυσικής λεπτομέρειας σε πολυπύρηνους επεξεργαστές αρχιτεκτονικής x86. Ο προσομοιωτής επίσης δρα ως αντικείμενο μελέτης για το πώς οι πολυπύρηνοι επεξεργαστές έχουν εξελιχθεί σε αρχιτεκτονική και συμπεριφορά, καθώς και βοηθά στην ανάλυση των δυνατών και αδύνατων σημείων των πολυπύρηνων επεξεργαστών, ώστε να διερευνηθεί ο ρόλος που μπορούν να έχουν στον τομέα της μοντελοποίησης δικτύων νευρώνων με μεγάλη υπολογιστική ισχύ.

Η διατριβή παρουσιάζει ολοκληρωμένα την ανάπτυξη του προαναφερθέντος προσομοιωτή. Το έργο ξεκινά με μια εφαρμογή ειδικά σχεδιασμένη για τους πρώτους πειραματικούς πολυπύρηνους επεξεργαστές. Καθώς η πολυπύρηνη αρχιτεκτονική εξελίσσεται, επαναπροσδιορίζουμε τις παραμέτρους και τον σχεδιασμό του προσομοιωτή με ακρίβεια προκειμένου να εκμεταλλευθούμε τις προόδους της εξελισσόμενης τεχνολογίας. Καθ΄ όλη τη διαδικασία, ο προσομοιωτής ενσωματώνει περισσότερες επιλογές μοντελοποίησης, υποστηρίζει μεγαλύτερο εύρος παραμέτρων προσομοίωσης και τελικά, λειτουργεί σε ένα σύγχρονο, κλιμακώσιμο

Abstract in Greek

πολυπύρηνο επεξεργαστικό σύστημα. Το τελικό προϊόν αυτής της διατριβής είναι ένας προσομοιωτής που αποτελεί μια αποτελεσματική λύση για τη μελέτη απαιτητικών μοντέλων νευρώνων, τόσο από άποψη υπολογιστικής επίδοσης αλλά και καταναλώσης ενέργειας.

Οι προσφορές μας στην επιστήμη του τομέα εστιάζονται στην ανάλυση των επιδόσεων των πολυπύρηνων επεξεργαστών όταν καλούνται να επεξεργαστούν μαθηματικά μοντέλα νευρώνων. Μέσω του προτεινόμενου προσομοιωτή, αναδεικνύουμε πώς το ευρύ φάσμα των παραμέτρων μοντελοποίησης νευρώνων επηρεάζει την προσομοίωση σε πολυπύρηνους επεξεργαστές. Ως εκ τούτου, κάνουμε ένα σημαντικό βήμα προς την αποτελεσματική αξιοποίηση υπολογιστικών συστημάτων υψηλών επιδόσεων με σκοπό την αντιμετώπιση των προκλήσεων που επιβάλλονται από τον τομέα της υπολογιστικής νευροεπιστήμης.

Σημαντικό κομμάτι της διατριβής ασχολείται με την ενσωμάτωση του προσομοιωτή σε μια ευρύτερη, συνεργατική, διαδικτυακή πλατφόρμα που στοχεύει στην εκτέλεση προσομοιώσεων μοντέλων νευρώνων με υψηλή επεξεργαστική ισχύ. Η πλατφόρμα που παρουσιάζεται, με την ονομασία "BrainFrame", αξιοποιεί ενα ετερογενές σύνολο από επιταχυντές, συγκεκριμένα πολυπύρηνους επεξεργαστές, κάρτες γραφικών και FPGA, προκειμένου να δώσει αποτελεσματικές λύσεις για διαφορετικές περιπτώσεις μοντελοποίησης και παραμέτρων δικτύου νευρώνων. Αποδεικνύουμε την αξία της πλατφόρμας μέσω της ανίχνευσης διαφορετικών περιπτώσεων προσομοίωσης όπου μια αλλαγή στον επιταχυντή που εκτελεί την προσομοίωση προσφέρει σημαντικά κέρδη στην ταχύτητα προσομοίωσης, υπογραμμίζοντας έτσι την αξία της ετερογένειας στην προσομοίωση μοντέλων νευρώνων με μεγάλη επεξεργαστική ισχύ.

# Acknowledgements

The entirety of my journey to the depths of academic research has been supervised by my professor Dimitrios Soudris, without whom not a single page of this document would have been made possible.

Three distinct people have aided me tremendously in the past 6 years of my research. Dr. Dimitrios Rodopoulos, Dr. Harry Sidiropoulos and Dr. Christos Strydis have been the best mentors and advisors anyone could ever ask for. They are also pretty cool people to hang out with.

I've had the pleasure of working closely with a good number of collaborators for my thesis. Soon-to-be-Dr. George Smaragdos, Prof. Mario Negrello, Konstantinos Katsantonis and Sotiris Panagiotou have been exemplary colleagues and helped shape this Doctoral thesis, particularly for our joint project of BrainFrame. Colleagues Alexandros Neofytou and Ioannis Magkanaris have contributed significantly in our collaborative efforts; it was a joy to help them graduate. Colleague Sofia Nomikou has helped me lay the groundwork on top of which I built my thesis.

I would like to acknowledge many people from both NTUA Microlab and Erasmus MC. A few distinct people amongst many are Prof. Chris I. De Zeeuw, Dr. Maro Baka, Dr. Dimitris Anagnostos, Dr. Robert Seepers, Dr. Georgios Zervakis, Dr. Sotiris Xydis, Konstantina Koliogeorgi and Zefi Skini.

I owe my eternal gratitude to my mom Despoina, my dad Theodoros, my brother Antonis, my grandfather Georgios and my beloved, sweet late grandmother Barbara. Thank you for supporting me for 30 years and loving me unconditionally.

May my furry best pal Homer forever chase after balls and bark at vacuum cleaners in dog heaven.

Finally, no man walks alone. I would like to close this section with the names of my dearest friends who have helped me shape who I am as a person and supported me emotionally through this tough journey: Dimitris, Vasilis, Thodoris, Mary, George, Ira, Kostas, Konstantinos, Julia and Daphne.

# Contents

| Abstract     |        |                                               |      |

|--------------|--------|-----------------------------------------------|------|

| П            | ερίλι  | ηψη Στα Ελληνικά                              | iv   |

| A            | ckno   | wledgements                                   | vi   |

| $\mathbf{C}$ | onter  | nts                                           | vii  |

| Li           | ist of | Figures                                       | X    |

| Li           | ist of | Tables                                        | xiii |

| 1            | Intr   | roduction                                     | 1    |

|              | 1.1    | Computational Neuroscience                    | 1    |

|              |        | 1.1.1 Challenges                              | 1    |

|              |        | 1.1.2 Motivation                              | 2    |

|              | 1.2    | Manycore Computing Systems                    | 5    |

|              |        | 1.2.1 Transition from Single-Core to Manycore | 5    |

|              |        | 1.2.2 Manycore Systems Progression            | 7    |

|              |        | 1.2.3 Modern Usage                            | 9    |

|              | 1.3    | Contributions in Computational Neuroscience   | 11   |

|              | 1.4    | Contributions in Manycore Computing           | 12   |

|              | 1.5    | Overview of the Doctoral Thesis               | 13   |

| 2            | Rel    | ated Work                                     | 14   |

|              | 2.1    | Human Brain Modelling                         | 14   |

|              |        | 2.1.1 Overview                                | 14   |

|              |        | 2.1.2 Integrate-and-Fire Models               | 15   |

|              |        | 2.1.3 Conductance-based Models                | 16   |

|              | 2.2    | High Performance Computing in Neuromodelling  | 17   |

|              |        | 2.2.1 In-Silico Experiments                   | 17   |

|              |        | 2.2.2 Neuronal Simulation Frameworks          | 18   |

|              |        | 2.2.3 Model and Network Description Tools     | 20   |

|              | 2.3    | Summary                                       | 22   |

| 3            | Neu    | romodelling on a Manycore Processor           | 24   |

*Contents* viii

|   | 3.1 | Introd    | uction                                               |

|---|-----|-----------|------------------------------------------------------|

|   |     | 3.1.1     | The Human Inferior Olivary Nucleus                   |

|   |     | 3.1.2     | InfOli Simulator                                     |

|   | 3.2 | Target    | Architecture                                         |

|   |     | 3.2.1     | The Single Chip Cloud Computer                       |

|   | 3.3 | Imple     | nentation                                            |

|   |     | 3.3.1     | Algorithm                                            |

|   |     | 3.3.2     | Platform Considerations                              |

|   | 3.4 | Evalua    | ation                                                |

|   |     | 3.4.1     | Experimental Setup                                   |

|   |     | 3.4.2     | Results                                              |

|   | 3.5 | Summ      | ary                                                  |

| 4 | Sca | ling th   | e Neuromodelling Application 40                      |

| * | 4.1 | _         | uction                                               |

|   | 4.2 |           | g to Intel Xeon Phi 1st Generation                   |

|   | 1.2 | 4.2.1     | Platform Architecture                                |

|   |     | 4.2.2     | Application Mapping                                  |

|   |     | 4.2.2     | 4.2.2.1 MPI Implementation                           |

|   |     |           | 4.2.2.2 OpenMP Implementation                        |

|   |     |           | 4.2.2.3 Hybrid Implementation                        |

|   |     | 4.2.3     | Experimental Evaluation                              |

|   |     | 4.2.5     | 4.2.3.1 Experimental Setup                           |

|   |     |           | 4.2.3.2 Evaluation                                   |

|   |     | 4.2.4     | Vectorized Implementation                            |

|   |     | 4.2.4     | 4.2.4.1 Basics of Vectorization                      |

|   |     |           | 4.2.4.1 Basics of Vectorization                      |

|   |     |           | 4.2.4.2 User-assisted Dependency Disamolguation (DD) |

|   |     |           | 4.2.4.4 Vectorization-Driven Loop Splitting (LS) 57  |

|   |     |           | 4.2.4.4 Vectorization-Driven Loop Splitting (LS)     |

|   |     |           | 9 ( )                                                |

|   | 4.9 | Dontin    |                                                      |

|   | 4.3 | 4.3.1     |                                                      |

|   |     | _         |                                                      |

|   |     | 4.3.2     | 11 0                                                 |

|   |     | 4.3.3     | •                                                    |

|   |     |           |                                                      |

|   | 4.4 | N / 1 + : | 4.3.3.2 Evaluation                                   |

|   | 4.4 | 4.4.1     |                                                      |

|   |     |           |                                                      |

|   |     | 4.4.2     | Scaling Considerations                               |

|   |     | 4.4.3     | Experimental Evaluation                              |

|   |     |           | 4.4.3.1 Experimental Setup                           |

|   |     | 1 1 1     | 4.4.3.2 Experimental Evaluation                      |

|   |     | 4.4.4     | Resource Allocation                                  |

|   | 4 = | 4.4.5     | Workload Parameters                                  |

|   | 4.5 | Summ      | ary                                                  |

Contents

| 5  | Het    | erogeneous Neurocomputing 87                  |

|----|--------|-----------------------------------------------|

|    | 5.1    | The Case for Heterogeneity Today              |

|    |        | 5.1.1 Challenges                              |

|    |        | 5.1.2 HPC Projects for Heterogeneity          |

|    |        | 5.1.3 Cloud Solutions                         |

|    | 5.2    | BrainFrame: Bringing HPC to Neuroscience      |

|    |        | 5.2.1 System Overview                         |

|    |        | 5.2.1.1 Integrated Platforms                  |

|    |        | 5.2.1.2 Middleware                            |

|    |        | 5.2.1.3 Frontend and Automation               |

|    |        | 5.2.2 Experimental Evaluation                 |

|    |        | 5.2.2.1 Experimental Setup                    |

|    |        | 5.2.2.2 Results                               |

|    |        | 5.2.3 Moving Forward                          |

|    | 5.3    | Summary                                       |

| 6  | Cor    | nclusions 110                                 |

|    | 6.1    | Thesis Summary                                |

|    | 6.2    | Thesis Highlights                             |

|    | 6.3    | Future Work                                   |

|    |        | 6.3.1 Framework Expansion                     |

|    |        | 6.3.2 Emerging HPC Technologies               |

|    |        |                                               |

| Bi | ibliog | graphy 117                                    |

|    |        |                                               |

| A  |        | pendix A. Publications                        |

|    |        | List of International Journal Publications    |

|    | A 2    | List of International Conference Publications |

# List of Figures

| 1.1  | grade manycore processor designed by Intel [1]. This particular model is a 7120p, a PCI-Express card that depends on a processor host in order to boot.                                                                                                                                                                                                               | 6        |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

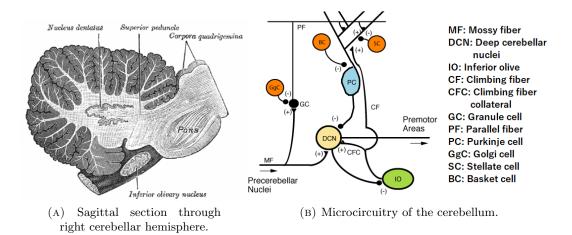

| 3.1  | Anatomical and circuit-level representations of the brain regions studied                                                                                                                                                                                                                                                                                             | 25       |

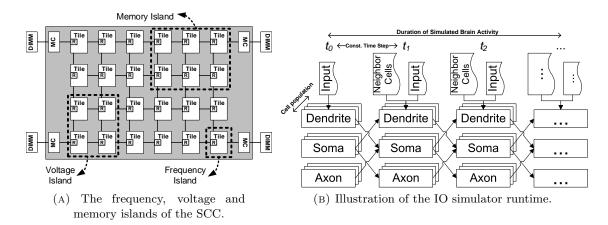

| 3.2  | High level view of the target platform and the target application that are discussed in this Chapter                                                                                                                                                                                                                                                                  | 28       |

| 3.3  | Illustration of IO neuron cell connectivity: the central cell is connected to the highlighted cells around it                                                                                                                                                                                                                                                         | 29       |

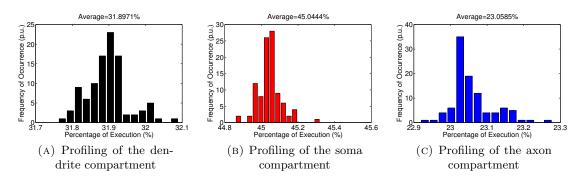

| 3.4  | Profiling of 100 iterations of the IO neuron cell model to extract timing information for each compartment                                                                                                                                                                                                                                                            | 30       |

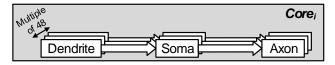

| 3.5  | The two mapping options of the IO neuron cell simulator on the SCC chip that are discussed in this chapter                                                                                                                                                                                                                                                            | 31       |

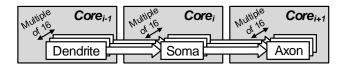

| 3.6  | Initial benchmarking with the SCC trained at $V_{dd} = 1.2 \text{ V}$ with a 533 MHz clock. The baseline represents a single-threaded version of the simulator,                                                                                                                                                                                                       | 0.1      |

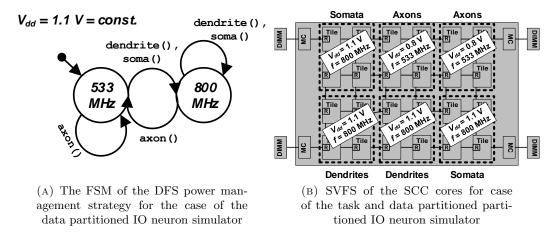

| 3.7  | running on a single SCC core with the above voltage and frequency Two power management schemes, tailored to the data and combined task and data partitioning mapping schemes                                                                                                                                                                                          | 31<br>32 |

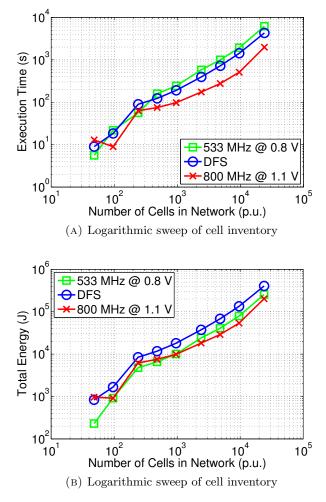

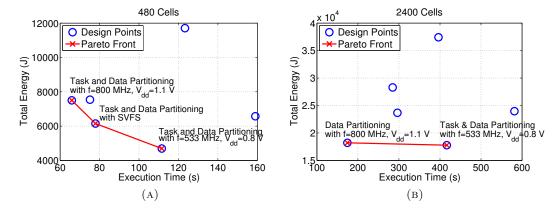

| 3.8  | Performance vs. quality cost assessment for different power management schemes of the strictly data partitioning mapping, for various neuron network sizes                                                                                                                                                                                                            | 34       |

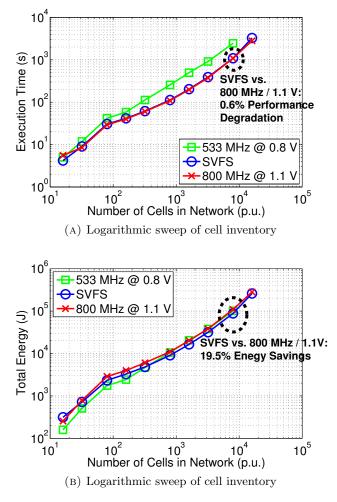

| 3.9  | Performance vs. quality cost evaluation for different power management schemes of the task and data partitioning mapping option, for various                                                                                                                                                                                                                          | 35       |

|      | cell network sizes                                                                                                                                                                                                                                                                                                                                                    | 37       |

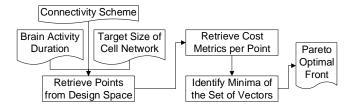

| 3.12 | front                                                                                                                                                                                                                                                                                                                                                                 | 37<br>38 |

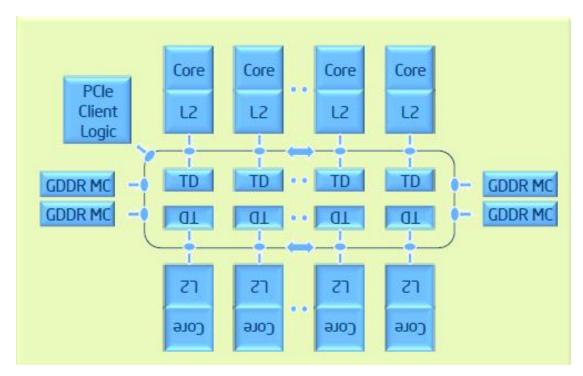

| 4.1  | The Knights Corner die organization [2]. The reader can notice the bidirectional ring that constitutes the communication avenue for the cores of the Knights Corner co-processor [1]. Each core is accompanied by a private L2 cache that is kept fully coherent by a global-distributed tag directory (TD). The bidirectional ring also connects to the PCIe bus and |          |

|      | to the GDDR5 memory via respective controllers                                                                                                                                                                                                                                                                                                                        | 42       |

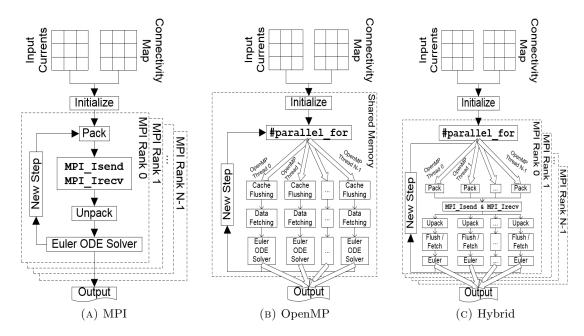

| 4.2  | Flowchart of the implementations discussed in this chapter [3]                                                                                                                                                                                                                                                                                                        | 44       |

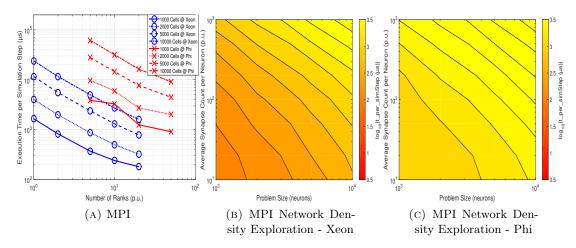

| 4.3  | Depiction of MITI measurements on the nost and the Phi                                                                                                                                                                                                                                                                                                                | 48       |

List of Figures xi

| 4.4  | Depiction of OpenMP measurements on the host and the Phi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 50 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

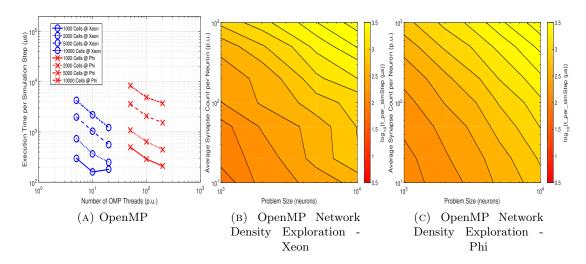

| 4.5  | OpenMP thread activity on the Xeon host                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 50 |

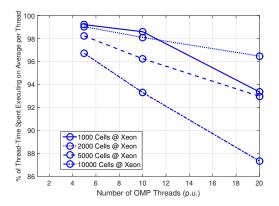

| 4.6  | Depiction of Hybrid measurements on the host and the Phi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 51 |

| 4.7  | Comparing the best implementations on host and accelerator, before man-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|      | ual AVX-oriented optimizations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 53 |

| 4.8  | An example of preventing aliasing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 56 |

| 4.9  | Using _mm malloc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 56 |

| 4.10 | Nested Loop example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 57 |

| 4.11 | Split Loop example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 57 |

| 4.12 | Data represented as a struct                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 59 |

| 4.13 | Data represented as multiple arrays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 59 |

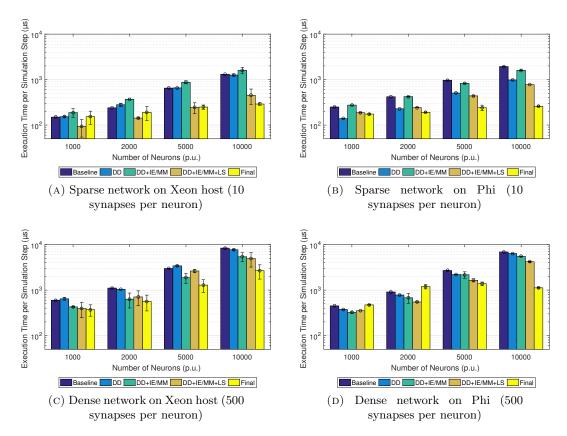

| 4.14 | Effects of vectorization on networks of varying size and complexity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 60 |

| 4.15 | Scaling up the best and properly vectorized implementation on the host and the accelerator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 61 |

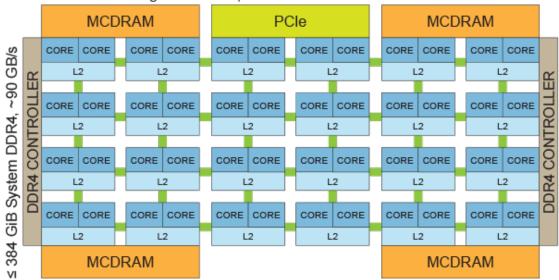

| 4.16 | The Knights Landing die organization [4]. Each tile consists of 2 cores that share an L2 cache. Inter-core communication is orchestrated as a mesh, in contrast to the previous generation (Knights Corner) which employed bidirectional rings [1]                                                                                                                                                                                                                                                                                                                                          | 63 |

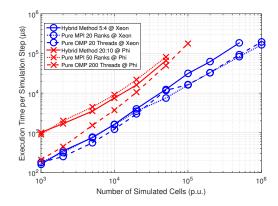

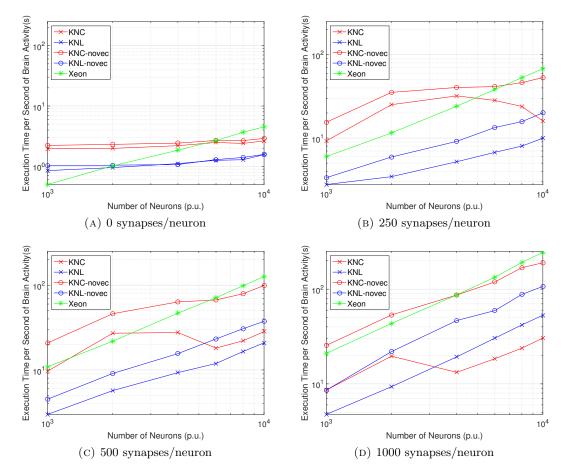

| 4.17 | Execution Time per second of simulated brain activity, comparison between KNC and KNL on different Simulator configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 67 |

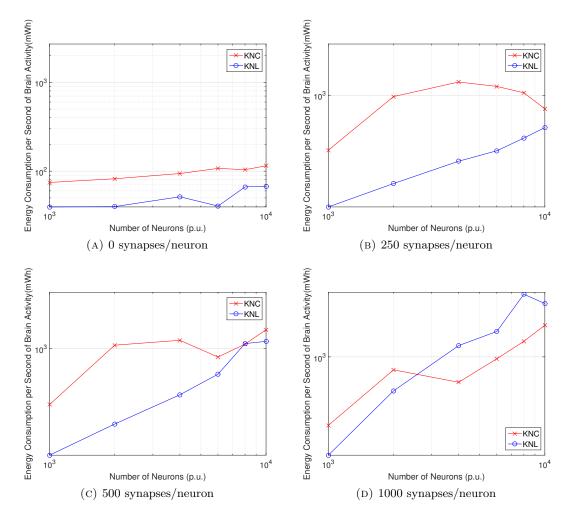

| 4.18 | Energy Consumption per second of simulated brain activity, comparison between KNC and KNL on different Simulator configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 68 |

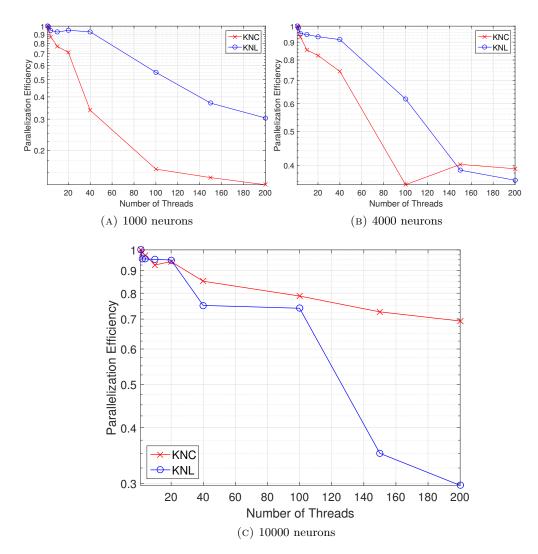

| 4.19 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 69 |

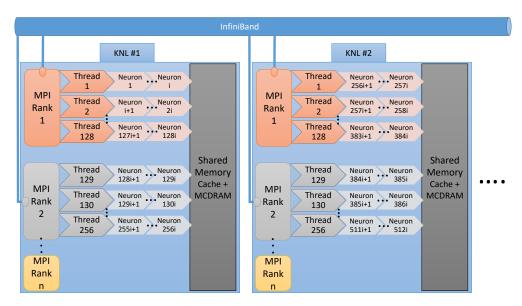

| 4.20 | Schematic of the simulator multinode implementation on the Knights Landing. In this example, each KNL processor operates at maximum capacity, meaning all of its $64 \times 4 = 256$ threads are employed, while a variable $n$ amount of MPI Ranks are spawned per platform. It should be noted that in our work, we opted for spawning $n = 4$ MPI Ranks per KNL platform. A number of $i$ neurons is assigned to each thread in this simulation, totalling a simulated network of $l = i \times 512$ neurons over two KNLs. The implementation schema can be extended to include as many |    |

|      | KNL machines as necessary and available                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 71 |

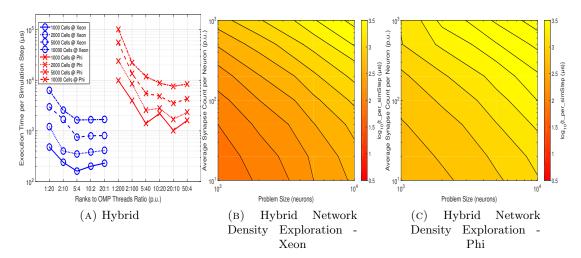

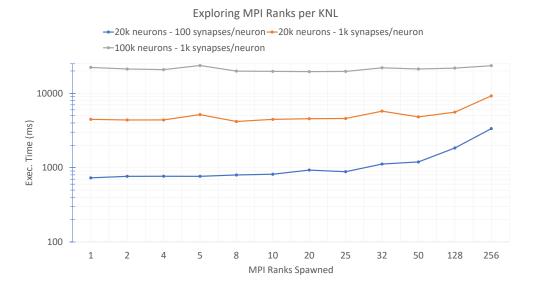

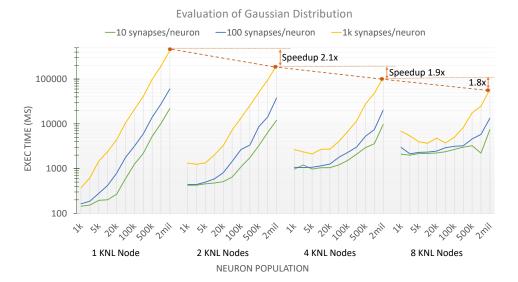

| 4.21 | Exploration of KNL's performance under different configurations of hybrid MPI-OpenMP clustering granularity. Three different networks of varying degrees in neuron population size and density are examined for 100 milliseconds of simulated brain time. We alter the amount of MPI ranks spawned on a single KNL processor. Configurations employing a small amount of MPI ranks exhibit superior performance. In particular, using 4 MPI ranks spawning 64 OpenMP threads offers good, reliable performance for all neuronal networks.                                                   | 73 |

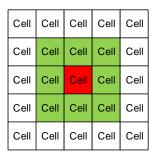

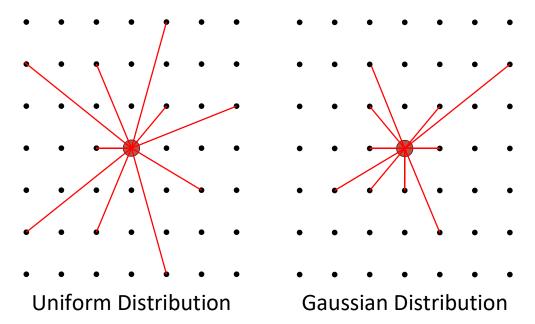

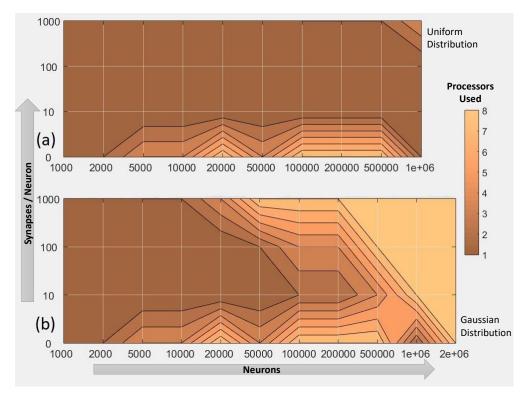

| 4.22 | Depiction of two different 7x7 2D neuron-meshes. In each case, the neuron in the center of the mesh forms 10 connections; the leftmost mesh follows a uniform distribution, whereas the rightmost features a Gaussian distribution. Uniform distribution creates spread-out connections, whereas the Gaussian distribution keeps the connections closer to their point of origin                                                                                                                                                                                                            |    |

|      | (i.e. neuron in the center of the mesh)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 76 |

List of Figures xii

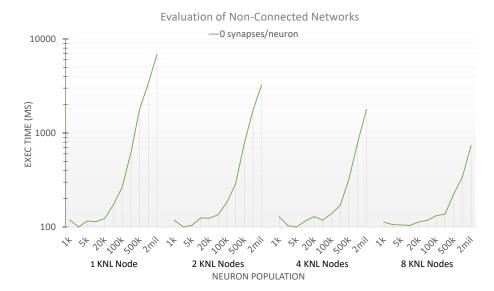

| 4.23       | Special use case of the simulator operating on non-connected networks. The neurons oscillate in a solitary environment. Due to the absence of communication between the cores' assigned subnetworks, this use case can be considered as one of the best cases for parallel processing from a scaling perspective. Utilizing increasing amounts of hardware scales simulation speed in an efficient manner; network simulation for 2 million isolated neurons requires execution time that is within the same order of |       |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 4.24       | magnitude as real time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 77  |

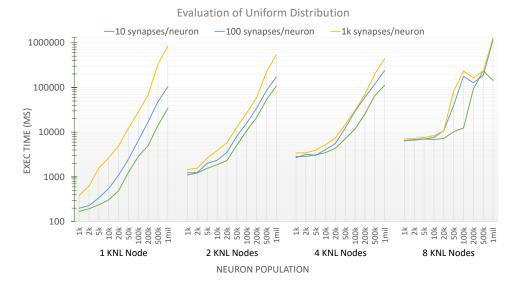

| 4.25       | for heavier workloads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 78  |

| 4.26       | with the amount of hardware employed. Smaller speedups are attained for sparser, smaller networks                                                                                                                                                                                                                                                                                                                                                                                                                     | . 80  |

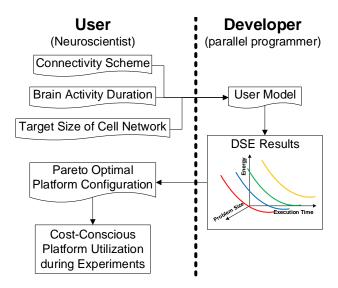

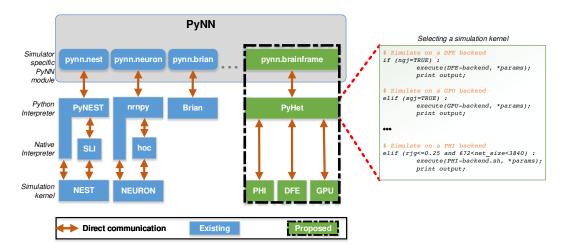

| 5.1        | PyNN architecture and the proposed BrainFrame framework [5]                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 95  |

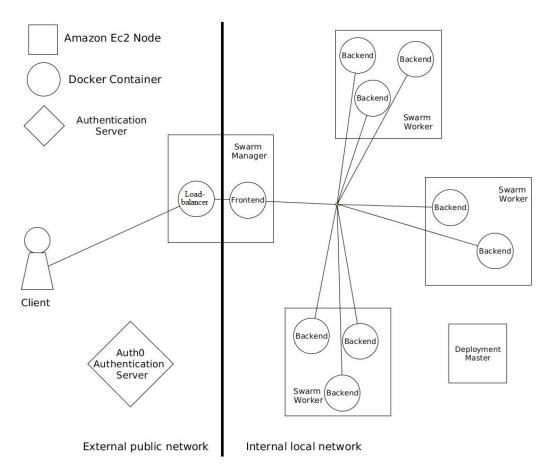

| 5.2        | An abstract schema of BrainFrame's Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 96  |

| 5.3        | A screenshot of the BrainFrame online service.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

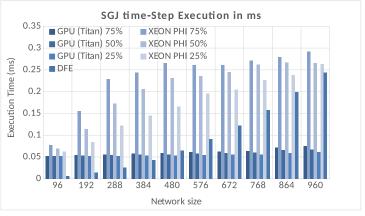

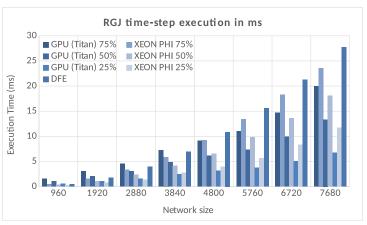

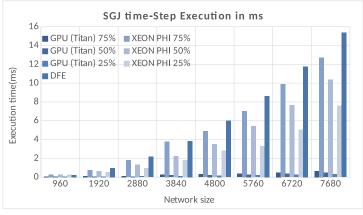

| 5.4        | Type I experiments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |

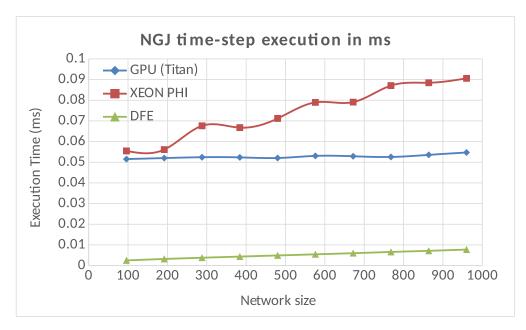

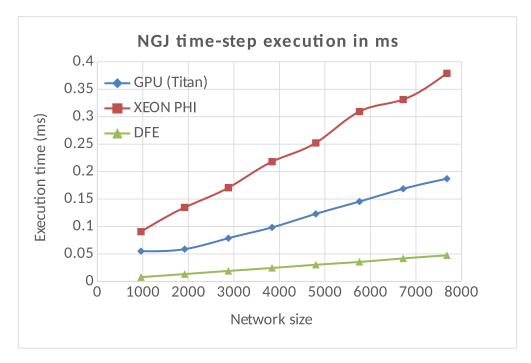

| 5.5        | NGJ execution time (TYPE I, no connectivity)                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

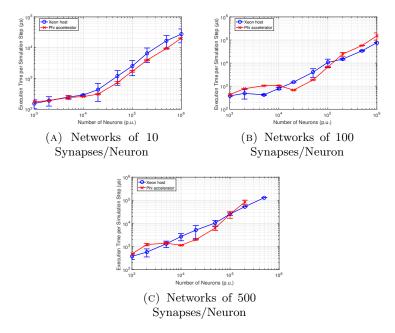

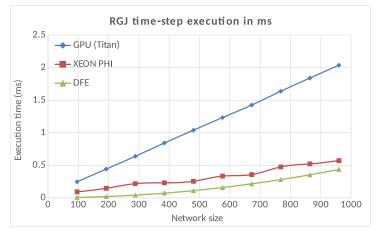

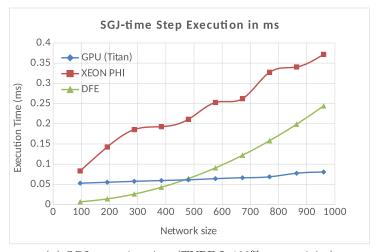

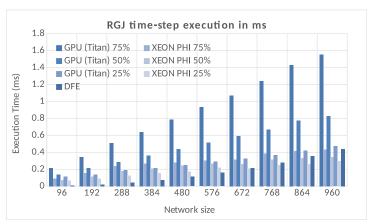

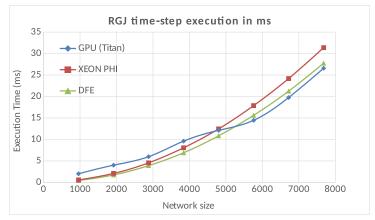

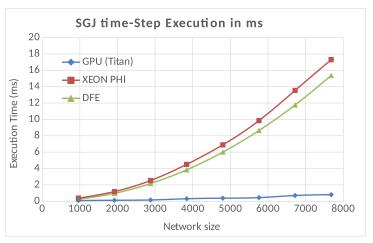

| 5.6<br>5.7 | Type II experiments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

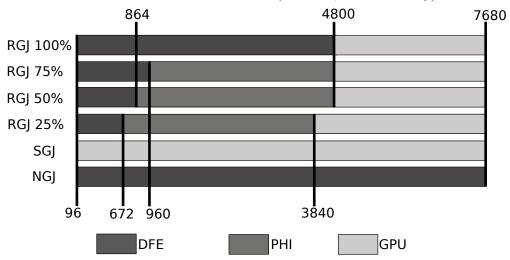

| 5.8        | BrainFrame accelerator-selection map for TYPE-II experiments. Selection is heavily dependent on the experiment, involving all three accelerator fabrics. For TYPE-I experiments, the DFE is always the optimal choice                                                                                                                                                                                                                                                                                                 |       |

|            | (not shown)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 107 |

# List of Tables

| 2.1 | Prior Art                                      | 23 |

|-----|------------------------------------------------|----|

| 4.1 | Parameter Space                                | 75 |

| 5.1 | Specifications of the accelerator fabrics used | 93 |

# Chapter 1

# Introduction

### 1.1 Computational Neuroscience

#### 1.1.1 Challenges

Computational neuroscience is an interdisciplinary field which encompasses studies of the brain's functionality and cognitive operations in conjunction with the advances of modern computer science. The field represents the advancement of knowledge concerning the world's most crucial phenomena, such as the human brain, through the aid of modern technology.

The last decade has witnessed a great amount of advances in the field of computational neuroscience. Neuroscientists have been gradually unveiling details of neuron operation. Using this knowledge, there is a wide research interest in studying the behaviour of single-neurons, as well as small networks of neurons and eventually brain-sized populations of neurons. Simulating these neuronal networks on various platforms is an active field of research; a major challenge is the sheer computational complexity that many of these neuron models entail.

Mapping the human brain, discovering its functionality and replicating its behaviour are all endeavours that entail multiple challenges and obstacles to overcome. The human brain is a particularly large and complicated organ. Compared to the rest of our biological organs, human knowledge is still in its infancy regarding how our brains operate. These factors lead to the existence of multiple mathematical approaches in an effort to model brain functionality. Each modelling effort has its own merits and shortcomings and all share a common trait: they require massive amounts of computations in order to simulate a meaningful portion of the brain's operations.

Massive computing power is necessary to calculate neuronal processes and their interactions, since our brain is comprised of billions of neurons [6]. The amount of information

that is exchanged within our formed neuronal networks is also vast due to the large amount of synapses, the "bridges" that connect the aforementioned neurons. This great volume of data needs to be modelled and interpreted in order to gain a grasp on how the human brain functions at a low, neuronal level.

The massive volume of calculations that are undertaken by the human brain is not the sole challenge that renders the neuroscientific field difficult to navigate. As science delves deeper into the complex nature of the human brain, hopes of replicating parts of its activity arise; and so does the need to design simulation systems that can respond within logical time limits. Ideally, the tools used to probe brain functionality would operate within the same time scale as our brains in real life. Such tools would lessen experimentation setup times and aid neuroscientists in designing complex, in-silico experiments that help unravel how the brain responds to real-time stimuli. In the future, designing simulation systems that survey and process the conditions under which a brain operates in real time can be a crucial step to achieving implantable monitoring devices.

Furthermore, computational neuroscience is a relatively young field of science. The first book produced by the field was only published in 1990 and edited by Eric L. Schwartz [7]. As such, it is a rapidly evolving field full of potential, with new approaches to new obstacles being invented frequently. Neuroscientists have a lot of options in their arsenal when tasked with studying a certain phenomenon and choosing which avenue to pursue for their given task and circumstances can be a daunting problem. This is a common problem in the discipline of mathematical modelling, where different degrees of complexity and scale can expose or obscure details of the studied phenomenon. Thus, the goal of exploring each modelling option's benefits and shortcoming becomes increasingly relevant in the young field of computational neuroscience.

While computational neuroscience is a young and emerging field, the domain of neuroscience itself has a long and rich history. Neuroscientists have amassed an impressive amount of knowledge concerning the human nervous system, its physiology, anatomical details and biology. This vast knowledge needs to be updated and translated to formats that are suitable to utilize in today's processors. The challenge of porting the existing wealth of resources to modern, cutting-edge processing systems is far from a trivial task. It is, however, a necessary task in order for the field of computational neuroscience to be able to exploit the technological advances of high-performance computing.

#### 1.1.2 Motivation

The intersection of two different domains, neuroscience and computer science, is aptly named "Computational Neuroscience" and aims at revolutionizing what is possible in the field of human brain studies.

In-vitro or in-vivo neuroscientific experiments are very costly, time-consuming and require testing on animals. They are also highly complex, often difficult to reproduce and offer limited access. Hence, constructing and exploring realistic simulations of biological neural networks on computing platforms has come across as a very viable and useful alternative for neuroscientists in recent years [8, 9]. The resulting discipline of computational neuroscience comprises a powerful tool in the hands of the community. It helps elucidate fundamental brain mechanisms underlying many obscure neurological maladies and guide possible new therapies. In-vivo and in-vitro experiments, while being traditional and powerful experimentation tools for neuroscience, inherently present the possibility of the experimental data to become contaminated (from factors such as the effects of anesthesia). Many of the complex brain-system dynamics that define biological behavior are hypothesized and many in-vivo or in-vitro techniques are not always able to provide the means to validate them. Such challenges further increase the value of in-silico experimentation.

For decades, scientists have been fascinated by the methods and computational capabilities of the biological brain. The US National Academy of Engineers has listed the simulation of the human brain as one of the Grand Engineering Challenges. Inspired by the scientific effort, engineers began to copy computational concepts found in the brain, which led to the creation of the first Artificial Neural Networks (ANNs) with the creation of the perceptron. ANNs do not execute commands sequentially like the typical Von Neumann computer, but each node (or neuron) in a neural network is a separate set of functions and they are all evaluated concurrently during execution. The relation between input and output is defined largely by the network size, topology and interconnectivity of the neurons. Interconnectivity could eventually be adaptive, thus, mimicking the behavior of biological systems. Eventually, more advanced versions of neural-network models were developed, based upon greater understanding of the biological processes. Spiking Neural Networks (SNNs) do not abstractly mimic biological-neuron behavior but outright simulate the computational behavior of brain processes. True to their biological counterparts, SNNs have the ability to encode information using the transfer rate, amplitude and spike-train patterns, which gives them more capabilities than traditional ANNs. As a result, they are currently heavily used to model the complex behavior of biological-brain systems in neuroscientific research.

Regardless of the plethora of models and execution platforms, there has been reduced emphasis on systematically optimizing the model execution on a many-core platform. Given the capabilities of modern computing systems, the degrees of freedom that are available to the community allow an aggressive exploration of the performance vs. quality-cost trade-off. This enables cost-conscious execution of biologically accurate neural models on multi-/many-core systems. There is significant potential using such systematic approaches, given the magnitude and energy budget [10] of computing infrastructure employed for brain modeling [11].

Ultimately, computational neuroscience attempts to use neuronal network models of various complexities, the accuracy of which can provide predictive behavior and insight, and exploit them to guide further biological experiments. Long-term advancement in computational neuroscience can hopefully lead to improved medical treatment of brain-related health issues, novel artificial-intelligence applications and groundbreaking computer architectures.

Computational neuroscience can advance our understanding of human cognitive abilities and brain functionality, as well as reveal opportunities for evolving the nature of computer architecture. On one hand, mapping the human brain allows for detecting the cause of brain-related health issues and possibly, reveal methods for repairing damage caused to our nervous system. On the other hand, there have been emerging processing systems designed after certain aspects of our brains' method of operation. Artificial intelligence has been growing in popularity and applicability in different domains and novel computer architectures seek to emulate the human brain's high degree of intercommunication and multi-tasking.

Despite momentous achievements in the simulation of large scale neural systems, the path ahead is no less daunting. In the last decade, the computational neuroscience literature has seen the publication of brain scale models that include numbers of neurons comparable with those of biological systems, or patches of brain with high level of detail. Izhikevich and Edelman [12] simulated the whole thalamocortical system with quadratic 2D models and simple synapses, the Blue Brain Project has simulated detailed networks of a whole reconstructed cortical column with compartmental models and detailed synaptic models [13], as well as Erik De Schutter et al, who produced a highly detailed model of the cerebellar granular layer [14]. Going forward, it is the stated goal of the human brain project of expanding on the work of the Blue Brain Project and simulating a whole brain. Many other large scale reconstruction and analysis projects should be expected in the future, examining both larger neuron populations and more detailed neuron models [15].

The projects named above should be taken as isolated 'proofs of principle', and even if the authors have searched parameter spaces, the parameter space of possible networks has barely been scratched. The goal of computational neuroscience is not only to simulate a single column or even brain, but enormous classes of possible virtual brains. Making matters worse, it is likely that the future will demand that these brains be hooked to sensors and actuators and be required to function in real time and closed-loops.

This type of work pushes multiple boundaries of knowledge and technology. On the knowledge front, it commits the computational neuroscientist to a level of detail of the representation that exposes the free or unknown parameters of the system. This includes both the procurement of biological data, and the exploration of the gigantic parameter spaces. In fact, biological measurements of neuronal parameters can only take us so far, since neural network parameter spaces are far from convex [16, 17], hence simply

measuring biophysical properties of neurons will not be sufficient to recreate plausible neurodynamics. To make matters worse, biological neurons are in continuous change [18], and future brain models will need to tackle the problem of changeability as well, introducing yet another level of computational demands on the simulation.

A caveat of large scale simulations often put forth is that the correct level of detail for simulating brains is not known. This alone should be taken as justification for maintaining an agnostic view on the "a priori" required level of detail of the simulation. It is not inconceivable that future models will continue to biological detail that is relevant in particular scientific domains, and hence this agnosticism is commendable. The best means to define that required level of detail is in the simulation of large scale systems and the comparison with reduced version, to gauge the contribution of the extra amounts of detail. The work of reducing a model to its essentials, often passes through understanding the implications of more complex assumptions, and hence, to simplify one often has to complexify.

Hence, we should predict that the computational requirements for future neurocomputational models will demand ever increasing computational resources, particularly in the problems of parameter space exploration, large network homeostasis and real time embedding of brain sized simulations.

## 1.2 Manycore Computing Systems

#### 1.2.1 Transition from Single-Core to Manycore

Traditionally, single-threaded programming has been the go-to programming model for most research-oriented applications, including modelling. Single-threaded is a relatively simpler programming paradigm which naturally fits the design of the modeller. Specifically in the realm of neuromodelling, GENESIS and Matlab have been extensively used to cater to the needs of the community [19–22]. Processors largely remained single-core as long as they were sufficient for the needs of the industry and academic research. However, with processors reaching their power consumption limits [23], it became increasingly apparent that continuous escalation of a single-core's clock frequency would be unsustainable and different avenues for gaining more processing power out of computing systems needed exploration.

Multi-core architectures have been a large step in the evolution of high-performance computing, as well as algorithm design. In 2001, IBM's Power 4 processor [24] is the first step for the well-established semiconductor chip maker in the realm of incorporating more than one core on a single die. In order to take advantage of having multiple cores on a chip, the paradigm of parallel processing was made necessary. While the concept of parallel programming greatly predates the design of industry-grade multicore

FIGURE 1.1: Image of the Xeon Phi Knights Corner Coprocessor, the first industry-grade manycore processor designed by Intel [1]. This particular model is a 7120p, a PCI-Express card that depends on a processor host in order to boot.

architectures [25, 26], a systematic approach to parallel coding and the corresponding shift in the coding paradigm was made more prevalent once keeping up with Moore's Law became an increasingly difficult goal to attend via single-core chips.

Multi-core processors focus on a mixture of single-threaded performance and a limited amount of independent cores available on the die for parallel processing. The cores remain relatively complex, integrating most of the technological advancements that decades of single-threaded processing have added to engineering knowledge. Multi-core processors continue to evolve and take up a large share of the modern processor market [27], increasing in processing power as well as energy efficiency [28].

As the necessity for massive parallel processing of unprecedented amounts of data grew in recent years in various fields, such as communication [29], finance [30] and life sciences [31], the industry responds with increased availability of computational resources on chip. As a continuation of Moore's Law in a different form, the amount of cores integrated in a single die has risen exponentially, with supercomputers making the Top 500 list (the "who-is-who list in the field of high performance computing" [32]) comprised of processors with continuously increasing cores-per-die. The term "manycore" computing has been coined for a sub-category of multi-core processors which place an emphasis on their high degree of parallel processing power, offering tens to thousands of independent processor cores and frequently stressing the quantity, over the complexity of their available computational resources.

#### 1.2.2 Manycore Systems Progression

Manycore computing systems have continuously increased the density of their computational power over the years; the amount of CPUs that can "fit" in a single die has been an escalating number over the past decade. An interesting case in manycore systems evolution has been Intel's line of products in the manycore genre.

The semiconductor chip manufacturer Intel started an early project in 2007 code-named Intel Tera Scale Computing Research Program, which aimed at providing its customers with unprecedented, for its era, amounts of potential processing power. A first prototype that emerged out of this project was the 80-core Polaris chip [33] which was aimed towards research and allowing engineers to work with massively parallel applications in practice, rather than in theory. The die contained 80 routers for its core communication needs and produced great peak computational performance per watt.

However, not all early members of the Tera Scale Program were successful products. Larrabee was a manycore chip originally designed to act as a GPU [34]. Larrabee used multiple in-order x86-based CPU cores that featured vector processing units for single-instruction multiple-data (SIMD) commands. In 2010, the chip was discontinued shortly after its production, unsuccessful in its original intended purpose of rivalling general-purpose GPUs [35].

A significant entry in the list of early manycore processors is the Single-Chip Cloud Computer (SCC), announced in 2010 [36]. The 48-core processor held interesting features such as adjustable scaling of operating voltage and frequency levels, as well as the ability to code using familiar parallel computing paradigms. Since its cores did not share memory, a message-passing API code-named RCCE [37] was used that had significant similarities to the well-established MPI library [38]. The product was shipped to multiple research facilities and universities for experimental development and has been extensively used in many academic fields, long after the discontinuation of its production [39, 40].

The early products of the Tera Scale Program culminated in Intel's "Xeon Phi" line of manycore processors. The processors focus on the availability of parallel computing resources and their ease of programming. The Xeon Phi products are based on x86 cores, which support traditional coding tools, thus being able to run software that has been developed for regular, industrial CPUs with minimal effort. Their ease of usage, which increased as the products matured and more generations were produced, allowed for an attractive alternative to the high-performance-computing standard platform, the GPUs.

The prototype of Xeon Phi products was the Knights Ferry platform, produced in 2010 [41]. The chip is a derivative of the Larrabee prototype and was offered as a PCIe card with 32 in-order cores at up to 1.2 GHz with four threads per core, 2 GB GDDR5 memory

and 8 MB coherent L2 cache (256 KB per core with 32 KB L1 cache). It was built at a 45nm process and had a power consumption of approximately 300W. Despite supporting only single-precision floating point instructions, its high peak processing power at 750 GFLOPS allowed it to be used for research purposes by establishments such as CERN [42].

Following the Knights Ferry prototype, the Xeon Phi line of products officially recognizes the Knights Corner chip as the first generation of the Xeon Phi manycore processors [1]. The Xeon Phi Knights Corner is a manycore co-processor; it is designed as a Pci-Express card that requires a host in order to boot. However, after booting, the co-processor can act autonomously, is reachable via SSH protocols through its host and operates with a custom, down-to-basics lightweight Linux image. The focus of the co-processor lies in its wealth of computing resources, with 61 available cores and 4 threads available per core, as well as a 512-bit-wide vector processing unit for SIMD instructions. The processor becomes the object of experimentation for many research fields [43–45].

The most mature product in the Xeon Phi line of processors was the Xeon Phi Knights Landing [4]. This manycore processor was a stand-alone processor offering significant peak performance and energy efficiency. Variations of the processor as a Pci-Express accelerator card were also produced, but discontinued and not offered to consumers. The processor had a significant impact in the industry, making the top ranks of Top500 supercomputer lists [46]. The Knights Landing processor offered more resources than its predecessors, simplified inter-core communication schemes by using a well-established mesh interconnection pattern and its instruction set allowed for binaries compiled for any x86-based architecture to run on the Knights Landing without any modifications. Its ease of usage, its efficiency and peak performance were marketed as the platform's strong points, particularly against competing general-purpose GPUs.

The Xeon Phi line of products was officially announced to be discontinued by Intel in 2018 [47]. However, the manufacturer is expected to fabricate manycore platforms in its upcoming, at the time of writing, Xeon processor line. Manycore processors have already been made widely available to the market by AMD via their "Ryzen Threadripper" line of products [48], based on AMD's "Zen" architecture [49], processors integrating up to 32 CPU cores and 64 threads in a single chip. In an effort to maintain market share dominance, Intel's "Skylake" architecture products are projected to integrate 28 cores and 56 threads on chip. The products maintain architectural design aspects from the Xeon Phi Knights Landing, such as the interconnection fabric "Omni-Path" for low-latency inter-node communication in multinode systems, an AVX-512 instruction set and vectorization processing units [50]. With the volume of CPU cores offered by a single chip being being continuously driven higher by important chipset manufacturers, manycore processing will remain a valuable resource for high-performance computing in the future.

#### 1.2.3 Modern Usage

Manycore processors are utilized in a variety of domains today. As the need for parallel processing of demanding datastreams continues to grow, manycore processors and GPUs offer an abundance of processing cores to be utilized in parallel fashion in order to satisfy the computational needs of such applications. There is a variety of manycore processor architectures being designed and used today.

An emerging category of specialized, manycore processors derive from neuromorphic chip design, a design philosophy that seeks to emulate the brain's functionality in order to solve problems in an efficient and reliable way. Such chips replicate the interactivity of thousands to millions of neural cells by integrating massive amounts of processing cores on a single die. A prominent example of this class of processors is IBM's TrueNorth [51, 52], a chip integrating more than 4,000 cores and a total of approximately 1 million programmable artificial neurons. The chip aims at great energy efficiency and has been successfully used for artificial-intelligence-oriented applications. Another manycore processor from the domain of artificial intelligence is Eyeriss [53], designed for the promising class of deep convolutional neural networks.

Supercomputers continue using manycore processors as their basis for achieving peak performance approaching the scale of Exaflops. One of the most dominant supercomputers at the time of writing, the Sunway TaihuLight [54] chinese supercomputer hosts a wide range of applications in its manycore RISC processors codenamed SW26010 [55–58]. The supercomputer's RISC processors allow for good performance per watt.

The Xeon Phi line of products, particularly the Knights Landing, is still used extensively in the industry. Since they support traditional coding tools, such as OpenMP [59] and MPI [38] libraries, their ease of usage marks the, now discontinued, platforms as attractive choices for researchers globally. Along with its processing power, the Knights Landing processors host simulators for various natural phenomena [60], complex mathematical calculations [61] and life-science-oriented applications [62].

For manycore processors, ease of usage plays an important role in their adoption rate. Today, a number of programming paradigms are available for manycore architectures. Specialized hardware, such as IBM's Truenorth which specializes in artificial-intelligence-related research, utilizes specific programming models designed for its intended usage [63]. Other manycore processors use general-purpose programming frameworks. Shared-memory applications favour OpenMP, whereas multinode, split-memory applications use message passing protocols between nodes, such MPI. Heterogeneous systems and applications that seek portability in different accelerator engines, such as both GPUs and x86-based manycore systems, encourage the usage of frameworks such as OpenCL [64] for compatibility across different accelerator architectures.

Given the advent of specialized accelerator fabric in modern High Performance Computing infrastructure, it is imperative that applications are well understood, especially in the context of the accelerating platforms that are utilized. Additionally, these applications are to be used in scientific research that is very dynamic and many times conducted by non-HPC experts. Moving forward, the goal should not be to over-optimize them, but keeping the programming effort moderate, resulting to short development times, while providing sufficient performance. These factors can be critical in achieving widespread usage of manycore accelerators and their potential processing power in research.

## 1.3 Contributions in Computational Neuroscience

#### Challenge I

Current approaches for experimentation in the field of neuroscience can be placed under two categories, each with significant challenges to overcome:

- (i) traditional in-vivo (or in-vitro) experimentation, which is very time-consuming, costly and requires significant lab equipment, training and experience by the researcher and

(ii) emerging in-silico experimentation, which has been mostly focusing on simpler mod-

- elling due to the computational demands of large-scale neuronal network simulation.

#### Solution I

This dissertation shall prove that efficient neuromodelling of high complexity, scale and detail can be achieved, as long as enough engineering effort is provided. The proposed system achieves simulation of 1second of brain activity in 10minutes of execution time of a very demanding workload (2million neurons with 1k synapses per neuron of a detailed, conductance-based model). Furthermore, engineering insights will be given in order to help navigate future neuromodelling applications towards more efficient implementations, stressing neuromodelling parameters that significantly impact simulation speed and efficiency.

#### Challenge II

Although there already exist multiple frameworks for neuromodelling, those who are focused more towards biophysically-accurate model simulation are older tools, which can be difficult to use without prior engineering and programming knowledge. This can prove challenging for users from the traditional neuroscientific domain.

#### $Solution \ II$

This dissertation ultimately builds towards a simulation framework that works as an online service, available to any scientist and requires no engineering effort since it is entirely hosted on cloud computing services. Experimentation via the framework is achieved through a Python-based modelling software package that is widely used in the neuroscientific community. The thesis provides a detailed synopsis of the proposed framework, a product of collaboration between the Microprocessors and Digital Systems Lab of the National Technical University of Athens and Neurasmus B.V.

## 1.4 Contributions in Manycore Computing

#### Challenge III

Application design in manycore processors meets a significant challenge generated by overheads due to thread-level and inter-node communication. For non-embarassingly parallel workloads, coherence-imposed delays can be prohibitive, particularly in the case of neuronal networks simulating rapid brain activity.

#### Solution III

In this dissertation, delays imposed by synchronization between computational resources in both single- and multi-node manycore systems are examined through numerous approaches, highlighting the most efficient solution for a category of workloads which are especially demanding and communication-heavy. Through a combination of methods, an efficient implementation is achieved that utilizes a small cluster of manycore processors in order to reach a level of performance previously achievable only by much larger and more expensive computing systems. In addition to simulating large, demanding networks, the design proposed in this thesis provides, throughout the generations of technology researched in this paper, a steady performance speedup ranging from  $10 \times 50 \times$ , depending on network configuration, when compared to simulating on more traditional processors with fewer multithreading capabilities and smaller core counts.

#### Challenge IV

There is a wealth of options for acceleration platforms that offer better potential performance (FPGAs) or have established a wider usage rate (GPUs) compared to manycore computing fabrics. For any engineer working on the field high performance computing, the challenge of picking suitable hardware for her application is significant and the role of manycore computing fabrics in this endeavour is relatively unclear.

#### Solution IV

In this dissertation, the benefits and hindrances of many core processors are well-defined and elaborately compared to other widely-used accelerator options. By integrating many core computing in an ensemble of different accelerator fabrics, their potential usage in the emerging world of heterogeneous computing is highlighted. Important speedup gains can be derived from switching between different hardware as computational platforms depending on the configuration of the simulated network, where in some cases a successful switch can result in more than doubling  $(2\times)$  the execution speed of the requested simulation. Furthermore, the designed framework presented in this dissertation operates on a cloud computing platform which can act as a prime candidate for efficient heterogeneous computing.

#### 1.5 Overview of the Doctoral Thesis

- In Chapter 1, the reader was introduced to the domain of computational neuroscience. An overview of the appearance and evolution of manycore computing was then provided. The contributions of this Doctoral thesis were summarized, both in the field of neuroscience and high-performance computing.